UiMOR – UC Riverside Model Order Reduction Tool Suite

Version 1.0

Principle

Investigator:

Dr. Sheldon Tan (PI)

Department of Electrical Engineering,

University of California – Riverside

Email: stan@ece.ucr.edu

Graduate Students:

Hai Wang, Duo Li, Boyuan Yan

Funding:

We appreciate the following funding agencies for their generous supports of this project.

· National Science Foundation, “CAREER: Career Development Plan: Behavioral Modeling, Simulation and Optimization for Mixed-Signal System in a Chip”, CCF-0448534, (CCF-0529754 and CCF-0731962, CCF- 0830304, for REU supplements), 6/1/2005-5/31/2011. PI: Sheldon Tan.

Project

Descriptions

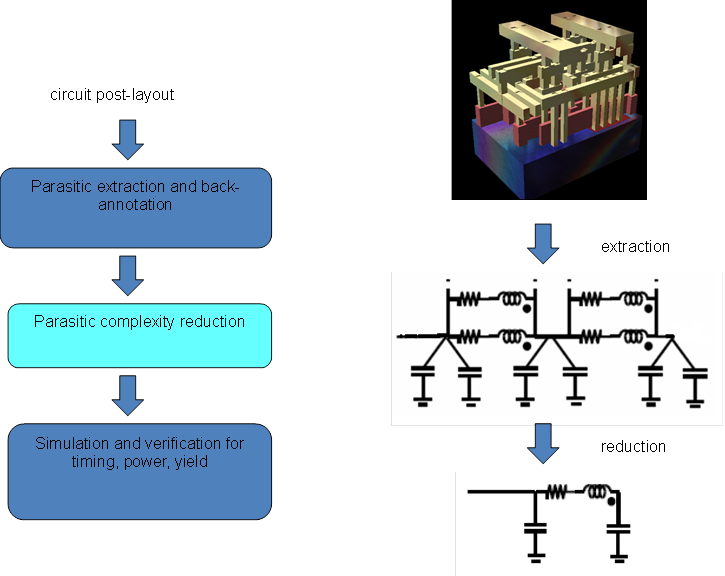

Complexity reduction is to reduce the interconnect circuit complexity while preserving accuracy of the original circuits to boost the verification process at the post-layout stage. It fills the emerging gap between the parasitic extraction and post-layout simulation by an increased number of parasitic components (resistance, capacitance, self and mutual inductance) required to model the physical reality of circuit interconnects, substrates, packages (see Figure 1). Circuit complexity reduction becomes indispensible as the complexity of nanometer integrated circuits, especially the unavoidable interconnect parasitics grow very rapidly (almost exponentially). This is driven by requirements of observing the finer levels of physic effects for accurate verification of increasing design concerns like noise, signal integrity, cross coupling, even quantum effects as technologies advance below 100nm. The massive extracted parasitics can significantly degrade performance of today’s SPICE-level commercial simulation tools. Excessive simulation time leads to long design time and large simulation tool budgets.

The reduction techniques for linear interconnect circuits have been studied intensively in the past and many techniques have been proposed. But existing techniques such as moment-matching based methods are mainly used for computing the interconnect delays and coupling noises in digital circuits. Those techniques lack the accuracy for the wide frequency ranges required by modeling analog, mixed-signal and RF circuits. Also the reduced models in the circuit matrix formats can’t be easily transformed back the circuit-level format compatible with the general circuit level SPICE format. Those reduction methods have to been integrated with the existing timing analysis tools to only compute the delay and noises of interconnects. As of now, the major EDA companies do not offer the stand-alone reduction tools, although there are startup efforts going on now to address this emerging market.

Figure 1 New post-layout verification flow

UiMOR is a new circuit complexity reduction tool developed by MSLAB at UC Riverside. UiMOR is a stand-along circuit complexity reduction tool. It can perform reduction accurate for wideband frequency range with negligible loss of accuracy and is well suitable for analog/mixed-signal/memory designs. It also works well for traditional delay and noise calculations in digital circuits as well.

UiMOR aims at reducing the amount of data in the netlist; reducing the memory footprint. As a result, it can speed up simulation without degrading simulation accuracy. UiMOR can take in the interconnect circuits modeled as RC/RLC circuits and produces the reduced RC/RLC circuits in SPICE format. Designers can specify the intended frequency range in which the reduced models will be accurate in its “analog” model for accurate reduction.

UiMOR has several features and advantages over the existing reduction techniques:

- Truly SPICE-in, SPICE-out

reduction technique and are SPICE compatible.

- Fit seamlessly with the

existing post-layout verification flow.

- First wide-band reduction

technique for digital, analog/mixed-signal/RF circuits designs.

- Can achieve 10-100X reduction

ratio and extremely efficient for RC circuits with very small accuracy

loss.

- Very scalable and efficient for

reducing interconnect circuits with million nodes.

The reduction techniques developed in UiMOR have the potential to bring immediate impacts on the VLSI chip design community as it can reduce the verification time of VLSI chip design, especially for the analog, mixed-signal and RF circuits, in the post-layout stages. The reduced simulation time can directly translate to improved efficiency and the saving in the simulation tool budgets and total design costs as few licenses are required and more simulation runs can be carried out for each design.

VSCLAB at UCR is leading the research efforts on the advanced circuit complexity redetection techniques, and we have developed several advanced circuit reduction techniques in the past few years. UiMOR was developed to specifically address the reduction problems in the analog/mixed-signal/memory/FPGA designs and we hope it can bring the visible benefits to the CAD research, development and circuit design communities.

Software Download

The software package, which includes the executable (redhat Linux 2.6.18-53.1.4.e15 version) version of UiMOR v1.0, user manual and some examples, can be found here.

Please send any problem, bug and comment regarding UiMOR to Sheldon Tan, at stan@ece.ucr.edu.

Relevant

Publications

B1. Sheldon X.-D. Tan and Lei He, Advanced Model Order Reduction Techniques for VLSI Designs, Cambridge University Press, 2007, ISBN-13 978-0-521-86581-4, ISBN-10 0-521-86581.